# Journal of Artificial Intelligence, Machine Learning and Data Science

https://urfpublishers.com/journal/artificial-intelligence

Vol: 1 & Iss: 1

**Research Article**

## Challenges in Verifying Complex SOC Designs

#### Niranjana Gurushankar\*

Citation: Gurushankar N. Challenges in Verifying Complex SOC Designs. *J Artif Intell Mach Learn & Data Sci 2022*, 1(1), 1907-1911. DOI: doi.org/10.51219/JAIMLD/niranjana-gurushankar/422

Received: 03 January, 2022; Accepted: 28 January, 2022; Published: 30 January, 2022

\*Corresponding author: Niranjana Gurushankar, Hardware Verification Engineer at Cisco Systems, USA

**Copyright:** © 2022 Gurushankar N., This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

### ABSTRACT

System-on-a-Chip (SoC) designs are now integral to modern electronics, enabling innovation in diverse fields such as mobile devices, automotive systems, and artificial intelligence. However, the relentless pursuit of increased functionality and performance has led to a surge in SoC complexity, posing significant challenges for verification engineers. This paper provides a comprehensive overview of the key obstacles encountered in verifying complex SoCs. We delve into the specific problems arising from increased design size, heterogeneity of integrated components, and the intricacies of verifying sophisticated functionalities. Furthermore, we examine the limitations of traditional verification methods and explore the potential of emerging methodologies such as formal verification, emulation, and assertion-based techniques. The paper also investigates the role of the Unified Verification Methodology (UVM) in streamlining SoC verification processes. Looking towards the future, we discuss promising trends, including the application of machine learning in verification, the integration of AI with formal methods, and the shift towards security verification. This paper aims to provide valuable insights for researchers and practitioners in the field of SoC verification, highlighting the critical need for continuous innovation to ensure the reliable and efficient design of future SoCs.

Keywords: System-on-a-Chip (SoC), SoC Verification, SoC Design, Design Complexity, Functional Verification, Power Management Verification, Security Verification, Simulation-Based Verification, Constrained-Random Verification, Emulation, FPGA Prototyping, Assertion-Based Verification, Unified Verification Methodology (UVM), Machine Learning (ML) for Verification

#### **1. Introduction**

SoC designs have become the cornerstone of modern electronics, revolutionizing industries from smartphones and wearable devices to automotive systems and high-performance computing<sup>1</sup>. By integrating diverse components like central processing units (CPUs), graphics processing units (GPUs), memory, and specialized intellectual property (IP) blocks onto a single chip, SoCs deliver unparalleled advantages in terms of miniaturization, power efficiency, and performance<sup>2</sup>. This integration trend is fueled by the ever-increasing demand for sophisticated functionalities in electronic devices, pushing the boundaries of SoC complexity to new heights. We now see SoCs with billions of transistors, intricate interconnections, and diverse on-chip communication protocols. However, this remarkable progress in SoC design brings with it a significant challenge: ensuring the correctness and reliability of these highly complex systems. Verification, the process of confirming that a design meets its specifications, has become a critical bottleneck in the SoC development cycle<sup>3</sup>. The sheer scale and heterogeneity of modern SoCs, combined with shrinking time-to-market windows, demand innovative verification approaches to avoid costly design flaws and respins<sup>4</sup>. This paper delves into the key challenges faced by verification engineers, exploring the specific issues arising from increased design size, the integration of diverse components with varying functionalities, and the difficulties in verifying complex algorithms and applications. We will examine the limitations of traditional verification methods and discuss the emergence of advanced techniques that aim to address these challenges.

#### 2. Challenges in SoC Verification

Verifying these complex SoCs is crucial to ensure correct functionality and avoid costly respins. However, several factors make this a challenging task:

#### 2.1. Increased Design Size and Heterogeneity

Modern SoCs can have billions of transistors, making it difficult to even comprehend the entire design, let alone verify it exhaustively<sup>5</sup>. SoCs integrate various IP blocks (e.g., CPU cores, GPUs, memory controllers, peripherals) from different vendors, each with its own specifications and communication protocols<sup>6</sup>. Ensuring these diverse components interact correctly and without conflicts is a major hurdle. For example, different IP blocks might have different clock domains or voltage levels, leading to synchronization and timing issues<sup>7</sup>.

#### 2.2. Functional Complexity

SoCs often implement complex algorithms for tasks like image processing, artificial intelligence, and cryptography. Verifying these algorithms requires specialized knowledge and extensive testing to cover all possible input combinations and corner cases. Imagine testing a self-driving car algorithm you need to consider countless scenarios like different weather conditions, pedestrian behavior, and unexpected obstacles<sup>8</sup>. SoCs are used in a wide range of applications, each with its own specific requirements and operating conditions. A mobile phone SoC needs to be verified for different cellular standards, multimedia applications, and power-saving modes.

#### 2.3. Limited Observability

SoCs have a deep hierarchy of modules and sub-modules, making it difficult to access internal signals for debugging<sup>9</sup>. It's like trying to find a problem in a complex machine without being able to open it up and see the inner workings. During simulation or emulation, it's often impractical to observe all signals simultaneously. This makes it challenging to pinpoint the root cause of errors, especially in complex interactions between different components.

#### 2.4. Verification Time Constraints

Companies face immense pressure to release new products quickly. Verification needs to be efficient and thorough to avoid delaying the product launch<sup>10</sup>. Simulating complex SoCs can take a very long time, even with powerful computers. This can create a bottleneck in the verification process.

#### 2.5. Power Management Verification

Modern SoCs have multiple power domains that can be turned on or off to save energy. Verifying that these power transitions happen correctly and don't cause data corruption or functional errors is crucial<sup>11</sup>. Clock signals can be gated (turned off) to reduce power consumption. However, improper clock gating can lead to timing violations and unpredictable behavior.

## 3. Methodologies for SoC Verification

To overcome the mounting challenges in SoC verification, engineers are increasingly turning to advanced methodologies that go beyond traditional simulation-based approaches. These methodologies leverage a combination of techniques, including,

#### 3.1. Formal Verification

Formal verification is a powerful technique used to prove the correctness of a design, ensuring it behaves exactly as intended<sup>12</sup>.

Unlike traditional testing, which relies on checking specific input scenarios, formal verification mathematically explores all possible states and behaviors of the design within a defined scope. To perform formal verification, engineers first create a formal model of the design, often using specialized languages that describe its behavior in a precise mathematical way. This model is then analyzed using powerful tools like model checkers and equivalence checkers. Model checkers are like automated inspectors that meticulously examine the design's state space, which is the set of all possible configurations it can be in. They check whether the design satisfies specific properties, usually expressed in temporal logic. These properties might be things like "the system will never deadlock," or "data will always be transferred correctly." If the model checker finds a violation of these properties, it provides a counterexample, highlighting the specific sequence of events that leads to the error. Equivalence checkers, on the other hand, are used to verify that two different representations of the same design are functionally identical. For example, you might use an equivalence checker to compare the initial RTL (Register-Transfer Level) description of a design with the optimized gate-level netlist generated by synthesis tools. This ensures that the optimization process hasn't introduced any unintended changes in behavior.

Formal verification offers several advantages. Its exhaustive nature can provide strong guarantees of correctness within the defined scope, significantly increasing confidence in the design. Moreover, it can find bugs early in the design cycle, even before simulation, saving time and resources. However, formal verification also has limitations. It can be computationally expensive for very large designs, as the number of states to explore grows exponentially. Additionally, it requires creating an abstract model of the design, which might not perfectly capture all the nuances of the actual hardware. Finally, it demands specialized expertise in formal methods and temporal logic, which may not be readily available in all design teams.

#### 3.2. Simulation-Based Verification

Simulation-based verification is the traditional workhorse of the verification world<sup>13</sup>. It involves creating a virtual model of the design and simulating its behavior using software tools. Engineers use testbenches to apply different input stimuli to the design and observe its outputs, checking if it behaves as expected. To make this process more efficient and effective, engineers employ techniques like constrained-random verification and coverage-driven verification. Constrained-random verification generates a wide range of input values while still adhering to certain rules or limitations, ensuring that the design is tested under diverse conditions. Coverage-driven verification, on the other hand, helps engineers track which parts of the design and its functionality have been tested. This ensures that no corner of the design is left unexplored and helps identify areas that need more attention. Simulation-based verification is highly flexible and can be applied to different levels of design abstraction and different design sizes. It also provides detailed visibility into the design's internal state during simulation, making it easier to identify the root cause of any errors. However, simulation has its limitations. Since it can't explore every possible scenario, it can't guarantee that all bugs have been found. Additionally, simulation can be time-consuming, especially for complex SoCs with billions of transistors. This can slow down the verification process and impact project schedules.

#### 3.3. Emulation and FPGA Prototyping

Imagine you're verifying a complex design, like a new graphics processor for a video game console. Simulation can be slow, like watching the game frame-by-frame. Instead, you could use specialized hardware to run the design at much faster speeds<sup>14</sup>. This is where emulation and FPGA prototyping come in. Emulation uses dedicated hardware that mimics the behavior of the actual chip. It's like having a super-fast version of the processor that lets you run the game at full speed and see how it performs in real-time. This is great for testing software and finding bugs that only show up under realistic conditions. However, emulation can be expensive and might not be able to handle extremely large designs.

FPGA prototyping involves implementing the design on a Field-Programmable Gate Array, which is a type of chip that can be reconfigured to perform different functions. This allows for faster testing than simulation and even lets you plug the FPGA into a real system to see how it interacts with other components. While not as fast as emulation, FPGA prototyping is generally more affordable and offers more flexibility. Both emulation and FPGA prototyping are valuable tools for verifying complex SoCs, especially when dealing with performance-critical designs or software integration. They provide a bridge between simulation and the actual chip, allowing engineers to catch bugs and optimize their designs more effectively.

#### 3.4. Assertion-Based Verification

Think of assertions as built-in alarms within your design. They're like little watchdogs that constantly monitor the design's behavior and bark if something goes wrong. Essentially, assertions are statements that express the intended behavior of the design, and they're embedded directly into the design's code<sup>15</sup>. During simulation or formal verification, these assertions are continuously checked. If an assertion "trip" - meaning the design's behavior doesn't match the expected behavior - it flags a potential bug. This is incredibly helpful because it catches bugs early on, often closer to the source of the problem, making it easier to identify and fix. It's like having a smoke detector that goes off in the exact room where the fire starts, rather than waiting for the whole house to fill with smoke.

Assertions also provide valuable clues about the nature of the bug, which speeds up the debugging process. They can tell you exactly what went wrong and when, giving you a head start in finding the root cause. However, using assertions effectively requires careful planning. You need to think about what properties are important to check and how to express them as assertions. Furthermore, assertions can't cover every possible scenario. They rely on the engineer's ability to anticipate potential problems and define appropriate checks. Like any alarm system, assertions are only as good as the rules they are programmed to follow. Despite these limitations, assertions are a powerful tool for improving verification efficiency and ensuring design quality. By embedding these "design intent" checks directly into the code, engineers can catch bugs early and debug them more effectively, leading to faster development cycles and more reliable products.

#### 3.5. Unified Verification Methodology (UVM)

The Unified Verification Methodology (UVM) provides a standardized and structured approach to building verification environments<sup>16,17</sup>. It offers a framework and a common language

for creating reusable and interoperable components, increasing efficiency and productivity in the verification process. Instead of starting from scratch, UVM provides a blueprint for organizing your testbench the environment used to test your design. This blueprint includes guidelines for creating different components with specific roles in the verification process. These components work together to stimulate the design with various inputs, observe its behavior, and check if the outputs are correct.

UVM also offers standardized ways to generate different types of input stimuli, ensuring that the design is thoroughly tested under various conditions. This helps uncover potential design flaws and ensures the design meets its specifications. One of the key benefits of UVM is reusability. Components can be reused across different projects, saving time and effort and allowing for a focus on the unique aspects of each design. UVM also promotes interoperability, meaning that components from different vendors can work together seamlessly. This expands the possibilities for building diverse and comprehensive verification environments. By providing this standardized framework and reusable components, UVM helps improve productivity and reduce verification time, leading to more efficient design verification.

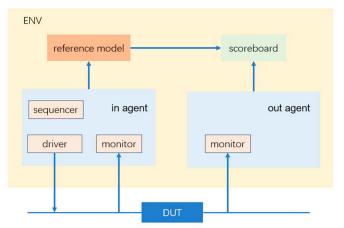

Figure 1: The structure of a basic UVM verification testbench<sup>22</sup>.

## 3.6. DUT (Device Under Test)

The Device Under Test, or DUT, is the heart of your verification effort. It's the actual design you're scrutinizing the intricate circuit, the complex system, the very thing you've poured your expertise into creating. Think of it this way: the DUT is the "black box" you're trying to understand. You want to know how it behaves under different conditions, if it meets the specifications, and ultimately, if it works as intended. In the UVM world, everything revolves around the DUT. It's the focal point of the entire verification environment. All the other components, all the tests, all the analysis - they all exist to interact with, observe, and ultimately assess the DUT. The DUT is stimulated with various inputs, its outputs are meticulously monitored, and its performance is rigorously checked against expectations. This comprehensive examination helps uncover any hidden flaws, ensures compliance with specifications, and builds confidence in the design's functionality. In essence, the DUT is the reason for the entire verification process. It's the star of the show, the subject of scrutiny, and the ultimate measure of success. Without the DUT, there's nothing to verify.

#### 3.7. Driver

The driver is a key component in the UVM framework, acting as the primary instigator of activity within your

verification environment. It's responsible for generating and applying inputs, or "transactions," to the DUT (Device Under Test). These transactions can range from simple data packets to complex commands and scenarios, simulating real-world interactions with the design. Think of the driver as the source of stimuli for your DUT. It's the component that injects energy and information into the design, prompting it to respond and behave in ways that can be observed and analyzed. The driver doesn't act alone, though. It takes its cues from another UVM component called the "sequencer." The sequencer provides high-level instructions about what kind of transactions to generate and when to send them. The driver then takes these instructions and translates them into the specific signals and data formats that the DUT understands. For example, if you're verifying a network interface card, the sequencer might instruct the driver to send a series of data packets with different sizes and contents. The driver would then take these instructions and create the corresponding packets, formatted according to the network protocol, and transmit them to the DUT through the appropriate interface. The driver's role is crucial in ensuring that the DUT is thoroughly exercised under a variety of conditions. By generating diverse and realistic stimuli, the driver helps uncover potential design flaws and ensures that the DUT meets its specifications.

#### 3.8. Monitor

In the world of UVM, the monitor plays the role of a vigilant observer, constantly keeping an eye on the DUT (Device Under Test). It's like a dedicated detective, meticulously recording every action and reaction of the design under scrutiny. The monitor passively observes the outputs of the DUT, capturing the streams of data and signals that emerge from its inner workings. 1 It doesn't interfere with the DUT's operation; it simply watches and records, much like a surveillance camera capturing events without influencing them. This constant observation generates a wealth of information about the DUT's behavior. It's like having a detailed log of everything the design does, every signal it sends, every state it transitions through. This data is invaluable for understanding how the design performs under different conditions and for identifying any anomalies or unexpected behaviors. The monitor's role is crucial in the verification process because it provides the raw data that other components use to analyze the DUT's functionality. For instance, the scoreboard relies on the monitor's observations to compare the actual outputs with the expected ones. Coverage groups use the monitor's data to track which parts of the design have been exercised.

#### 3.9. Scoreboard

The scoreboard in UVM is like the ultimate judge in your verification environment. It plays a crucial role in determining whether your design, the DUT, is functioning correctly. Think of it as the final arbiter, carefully comparing the actual outputs of your design with the expected results. The scoreboard receives information from the monitor, which, as we discussed, observes the DUT's outputs. It also has access to a "golden model" or a set of predefined expectations for how the DUT should behave under different conditions. With this information in hand, the scoreboard meticulously compares the actual outputs with the expected ones. It checks if the data matches, if the timing is correct, and if the overall behavior aligns with the design specifications. If everything lines up perfectly, the scoreboard gives a green light, indicating that the DUT is performing as intended. However, if there's a mismatch, the scoreboard raises a red flag, signaling a potential issue that needs further investigation. The score board's role is critical in ensuring the quality and reliability of your design. It acts as an independent verifier, providing an objective assessment of the DUT's functionality. By catching discrepancies and highlighting potential errors, the scoreboard helps you identify and address design flaws early in the verification process.

#### 4. Future Trends in SoC Verification

#### 4.1. Machine Learning (ML) for Verification

Machine learning is set to revolutionize how we verify chips<sup>18</sup>. ML algorithms can analyze vast amounts of data generated during simulation, emulation, and formal verification. They can learn to identify patterns that indicate bugs, predict which areas of the design are most likely to have issues, and even suggest solutions. This means faster, more efficient verification, and potentially even catching bugs before they appear!

#### 4.2. Formal Verification with AI

Formal verification, a powerful technique that mathematically proves design correctness, is getting a boost from AI<sup>19</sup>. This powerful combination will help us tackle even larger and more complex designs, ensuring they're rock-solid. AI algorithms can be used to guide formal verification tools, focusing their efforts on the most critical areas of the design. They can also help abstract the design, making it easier to analyze. AI can make formal verification more practical for large and complex SoCs.

#### 4.3. Shift-Left Verification

Traditionally, verification happens after the design is mostly complete. Shift-left verification aims to move it earlier in the design cycle, even to the architectural stage<sup>20</sup>. This involves using techniques like formal verification and virtual prototypes to verify the design at a higher level of abstraction, before detailed implementation. The advantage of this method is finding bugs early can significantly reduce the cost and effort of fixing them. Verification feedback can be used to improve the design architecture, leading to a more robust and efficient final product.

#### 4.4. Security Verification

With the increasing number of connected devices and the growing threat of cyberattacks, security verification is becoming paramount<sup>21</sup>. This involves specialized techniques to verify security features like encryption, authentication, and access control. It also includes identifying potential vulnerabilities that could be exploited by attackers. Enhanced security helps ensure that SoCs are resistant to cyberattacks and protect sensitive data. Helps mitigate the risk of security breaches and their associated consequences.

#### 5. Conclusion

In conclusion, the journey of verifying complex SoC designs is a continuous and demanding pursuit. These intricate systems, with their billions of transistors and diverse functions, push verification engineers to their limits. Ensuring these chips are reliable requires a multifaceted approach to tackle issues like design complexity, limited observability, and tight deadlines. The industry is rising to the challenge with advanced techniques. Formal methods mathematically prove correctness,

while simulation explores design behavior. Hardware-assisted methods like emulation offer faster speeds and system-level testing. Tools like assertions and the UVM framework help catch bugs early and improve efficiency. Looking ahead, exciting trends like machine learning will revolutionize SoC verification. Imagine algorithms that analyze vast amounts of data, find hidden patterns, and predict potential problems. AI can also enhance formal verification, making it applicable to even more complex designs. And by shifting verification earlier in the design cycle, we can catch bugs sooner. In a world increasingly reliant on connected devices, security verification is crucial. Specialized techniques are needed to ensure these chips are safe from cyberattacks. Ultimately, continuous innovation is key to keeping pace with the evolving challenges of SoC verification. By embracing new technologies and methodologies, we can ensure the reliability and security of the chips that power our future.

#### 6. References

- 1. Jerraya A, et al. System-on-Chip Design and Test: methodologies and design examples. Springer Science and Business Media, 2016.

- 2. Hennessy JL, Patterson DA. Computer architecture: a quantitative approach. Elsevier, 2011.

- Gielen G. CAD tools for embedded systems. In Embedded Systems Design. Springer, Boston, MA, 2007;19-38.

- Bahadur V, et al. System-on-Chip verification challenges and solutions. In Proceedings of the 47th Design Automation Conference. ACM, 2010;653-658.

- 5. Moore GE. Cramming more components onto integrated circuits. Electronics, 2006;38:114-117.

- Keutzer K, et al. System-level design: orthogonalization of concerns and platform-based design. IEEE Transactions on Computer-Aided <sup>1</sup> Design of Integrated Circuits and Systems, 2000;19:1523-1543.

- Semiat Y, Ginosar R. Timing measurements of synchronization circuits. IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, 2003;11:101-109.

- 8. Drechsler R. Advanced formal verification. Springer Science and Business Media, 2000.

- 9. Taylor S. The challenges of verifying complex systems. In Proceedings of the 43rd annual Design Automation Conference, 2006;843-848.

- Mishra P, Dutt ND. Functional verification of programmable embedded processors: a top-down approach. Springer Science & Business Media, 2005.

- Benini L, De Micheli G. Dynamic power management: design techniques and CAD tools. Springer Science and Business Media, 2012.

- 12. Clarke EM, et al. Model checking. MIT press, 2018.

- 13. Bergeron J, et al. Writing testbenches using SystemVerilog. Springer, 2011.

- Chen Z, et al. FPGA-based prototyping methodology for ASIC design. In Proceedings of the 2013 International Conference on Field-Prorammable Technology, 2013;181-188.

- 15. Foster H, et al. Assertion-based design. Springer Science and Business Media, 2011.

- 16. Accellera. Universal Verification Methodology (UVM) 1.1 Class Reference, 2011.

- 17. Spear C. SystemVerilog for verification: a guide to learning the testbench language features. Springer Science and Business Media, 2012.

- 18. Sharma A, et al. A survey on applications of machine learning in verification. Journal of Systems Architecture, 2021;117:102118.

- 19. Roy P. Formal verification with machine learning: a survey, 2019.

- 20. Cadence Design Systems. Shift-Left Verification: The Key to Faster SoC Design. White paper, 2018.

- 21. Zorian Y. Hardware security verification: A survey. IEEE Design and Test, 2017;34:6-18.

- 22. Bergeron J, et al. Writing Testbenches using SystemVerilog. Springer, 2011.